한 때는 컴퓨터가 방 전체를 가득 차지하고 라디오 수신기는 세탁기만큼이나 컸다. 최근 수십 년 동안 전자기기의 크기는 상당히 줄어들었고 이러한 추세는 막대한 비용과 에너지의 절감뿐 아니라 속도의 증가를 이끌며 지속될 전망이다.

이와 같이 기기의 크기를 축소하는 기술의 핵심은 테라스케일(Terascale) 컴퓨팅으로, 초당 수조 번의 작업을 수행 할 수 있는 단일 마이크로 칩에 의해 지원되는 초고속 기술이다.

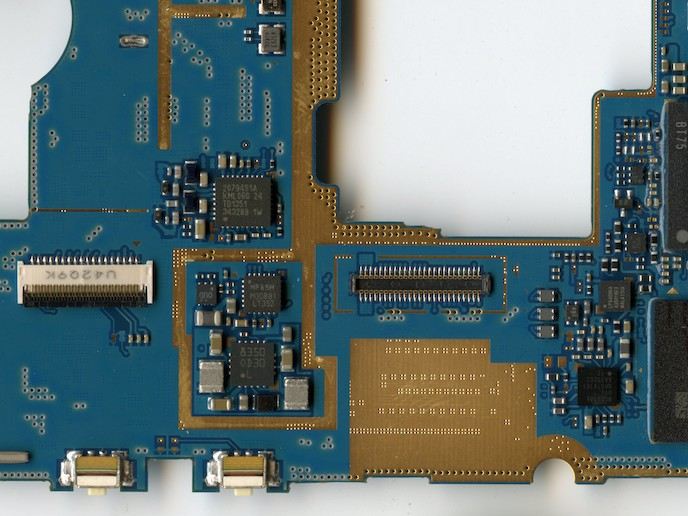

테라스케일(Terascale) 기술을 사용하여 모든 종류의 전자기기의 집적 회로를 만드는 데 일반적으로 사용되는 반도체 부품은 몇 년 내에 10 나노미터 미만을 측정 할 수 있게 될 것이다. 나노미터가 1미터의 10 억분의 1 미만인 것을 고려하면, 전자기기는 극도로 소형화될 가능성이 있고 오늘날보다 훨씬 적은 양의 에너지를 필요로 할 것이다. 즉, 이러한 개발은 전자기술 산업계에 대변혁을 일으킬 것이다

그러나 이러한 초소형 기기를 생산하기 위한 기술은 지속적인 발전에도 불구하고 신뢰성을 확보하기까지 갈 길이 멀다. 이를 위해 유럽연합이 자금을 지원하는 프로젝트인 TRAMS(Terascale reliable adaptive memory systems)는 칩 설계를 개선하여 신뢰성 향상을 도모했다.

연구팀은 오류 발생 가능성이 훨씬 낮은 칩 회로를 개발하기 위해 변동성 및 신뢰성 분석을 심도 있게 수행했다. 이 회로는 현재 신뢰성이 확보되지 않는 나노 소자에서 신뢰성 있는 메모리 시스템을 생산하는 새로운 설계를 특징으로 한다.

프로젝트의 주요한 도전은 5 나노미터 미만의 크기를 측정할 수 있는 개별 트랜지스터로 다양한 신기술을 사용하여 안정적이고, 에너지 효율이 뛰어나면서도 비용이 너무 크지 않은 컴퓨팅을 가능하게 하는 것이다.

이 팀은 테라스케일(Terascale) 컴퓨팅을 실현할 수 있는 가능성을 가진 다음의 기술들과 물질들을 조사했다.

- 탄소 나노튜브(Carbon nanotubes, 극소형의 원통형 나노구조 그래핀 기술)

- 핀 전계 효과 트렌지스터 공정(FinFETs)과 같은 새로운 트랜지스터 기하(입체) 구조

- 최첨단 나노 와이어(State-of-the-art nanowires), 신세대 전자기기에 사용하기 위해 매우 발전한 트랜지스터 기능을 제공

연구진들은 이 모델을 사용하여 기술에서 회로 수준에 이르는 신뢰성을 분석했다.

이러한 발전은 오늘날 반도체의 표준인 '상보적 금속 산화물 반도체'(CMOS, complementary metal-oxide semiconductors)를 재정의할 것으로 예상된다. 이 팀의 연구결과는 유럽 제조업체들이 16나노미터 범위 이하의 CMOS 장치를 개발하는 데 도움이 될 것이다. 가장 큰 도전은 CMOS 장치를 5나노미터 미만으로 줄이는 것이며 이 개발은 현재 가능성이 엿보이고 있다.

통신, 보안, 운송 및 산업에 이르기까지 미래의 CMOS 기반 장치들은 급격한 에너지 및 비용 절감을 수반하며 우리가 사용하는 기술을 재설계할 것으로 기대된다.

TRAMS 컨소시엄에는 스페인의 과학기술대학교(Universitat Politècnica de Catalunya)가 주관기관으로, 벨기에 및 영국의 대학과 회사가 파트너로 참여했다.